- 在高級流程節點上,隨機造成的效率損失成本數十億美元

- 當前的過程控制方法不足以解決隨機故障

- 新的白皮書描述了設計和測量解決方案以縮小隨機差距

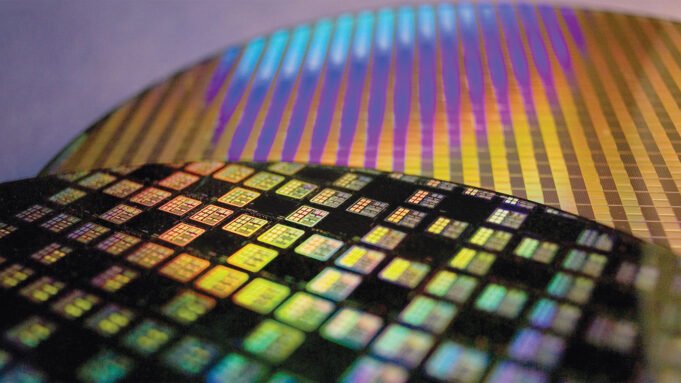

一份新的白皮書認為,由於他們聽說過的領域外,半導體行業正在損失數十億美元:周到的波動。

現在,這種形式的隨機設計變體被認為是在最先進的過程節點中實現高產量的最大障礙。

該文件由德克薩斯州的Fractilia貢獻,其首席技術官克里斯·麥克(Chris Mack)指出:“隨機波動率在引入大型批量構建的高級流程時會導致數十億美元的延遲”。

影響性能,性能和可靠性

Mack進一步解釋了當前的程序控制策略無法處理這些隨機結果。

麥克說:“縮小隨機差距需要完全不同的方法,即設備製造商需要驗證和採用的方法。”

Fractilia將這一“隨機差距”定義為研究中可以塑造的差異以及在可接受的回報中可靠產生的內容之間的差異。

在這個間隙的中心,有一個隨機植根於芯片生產中使用的材料,分子和光源的物理學。

儘管這些結果曾經可以忽略不計,但他們現在消耗了施工錯誤預算的越來越多。

麥克說:“我們已經看到,客戶在研發中的密集特徵很小至12納米。” “但是,當他們試圖將其移至施工時,隨機故障會影響他們實現可接受的性能,性能和可靠性的能力。”

該問題與EUV和高NA EUV光刻的興起並行。這些進步使芯片製造者能夠嘗試更小的功能,但也使他們更容易受到沉思的缺陷。

與傳統的波動率不同,這種類型的類型無法通過更嚴格的控制措施消除,必須通過設計和測量技術對其進行處理。

麥克說:“整個行業的差距是一個問題。” “這個問題可以最小化和測試,但這一切都始於精確的樓梯測量技術。”

白皮書,您可以下載 這裡它包括對問題的分析,並提出了隨機的設計,材料的創新以及該過程的更新作為向前路線。