- Apollo 2開關在單個混合動力芯片中支持Gen 6.2和CXL 3.1

- XConn想要重新定義帶寬的限制,但現實世界的結果仍然完全毫髮無損

- 英特爾和XConn共同努力測試基於PCIE的生態系統中的完整堆棧兼容性

XCONN Technologies正在準備證明其所描述的完全集成的內容,最終到PCIE GEN 6.2和CXL 3.1解決方案在即將到來的內存和存儲事件(FMS25)中。

該公司將啟動作為滿足AI工作量和數據中心的工作量需求的關鍵步驟。

但是,與早期技術的任何演示一樣,現實世界的擴展和信譽仍然是開放的問題。

具有理論靈活性的混合開關

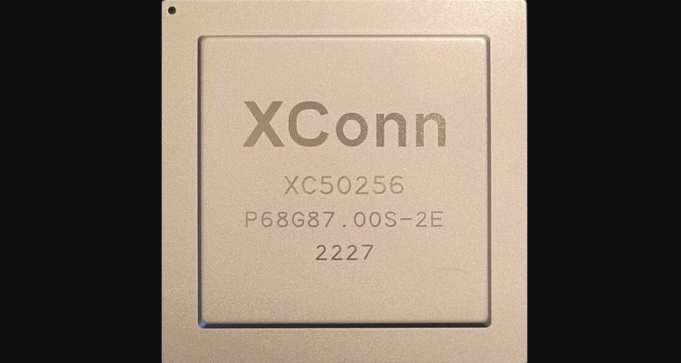

該公司的Apollo 2 Switch將是這一啟示的核心 – 作為業內的第一個混合動力開關,可以在單個芯片中支持PCIE Gen 6.2和CXL 3.1,據說可以簡化互連和增強計劃。

XCONN Technologies首席執行官Gerry Fan表示:“ Xconn很高興將PCIE Gen 6.2和CXL 3.1開關帶入現在的樣品。”

“隨著行業以更高的記憶和效率加速建築,我們的承諾是增強客戶最好的班級。”

這些好處旨在降低數據中心的複雜性,同時允許更廣泛的建築靈活性。

儘管在技術上很有希望,但這種集成的實際優勢將取決於工作 – 塔克斯的績效結果。

Xconn與之合作 英特爾還將其定位為重要的發展,因為根據英特爾高級Ronak Singhal的說法,該合作將有助於確保軟件和材料都可以平穩地相互作用,從而提供“從頭到尾提供強大的解決方案”。

公司期望這項努力為PCIE和CXL技術促進可互操作的環境。

儘管如此,該行業以前的經驗表明,成功的驗證通常需要時間和一個以上的演示週期。

即將到來的演示將顯示低範圍的高範圍區域延遲,突出顯示基礎架構的準備就緒,例如AI/ML模型,雲計算機和復合基礎架構。

據報導,XCONN PAVILION將提供完整的標準,但是在參考點發布之前,與現有的PCIE Gen 5 Developments相比,很難確定用戶可以等待多少。

XCONN還與ScaleFlux合作,以改善AI和雲基礎架構的CXL 3.1互操作性。

儘管這表現出動力,但它並未證實解決方案與當今建築師強調的工作負載類型的結合程度。

如果技術提供的話,高速存儲的後果很重要。

隨著對更大的SSD功能和更快的SSD性能的需求不斷增長,PCIE Gen 6可以支持存儲和加工廠之間的更快數據傳輸。

儘管如此,這些理論利潤必須通過懷疑主義來減輕,直到現場數據證實影響。

XConn演示可以標記AI材料下一章的開始。但是目前,它仍然是預覽,而不是證明點。

通過 TechPowerUp